— O veículo de teste de três camadas é um marco importante porque demonstra. Viabilidade de combinação de ligação híbrida e vias de silício de alta densidade

DENVER – 31 de maio de 2024 – Os cientistas do CEA-Leti relataram uma série de sucessos em três projetos relacionados no ECTC 2024 que são passos fundamentais para permitir uma nova geração de sensores de imagem CMOS (CIS) que podem explorar todos os dados de imagem para perceber uma cena , compreender a situação e intervir nela – capacidades que exigem a incorporação de IA no sensor.-

A demanda por sensores inteligentes está crescendo rapidamente devido às suas capacidades de imagem de alto desempenho em smartphones, câmeras digitais, automóveis e dispositivos médicos. Esta demanda por melhor qualidade de imagem e funcionalidade aprimorada pela IA incorporada apresentou aos fabricantes o desafio de melhorar o desempenho do sensor sem aumentar o tamanho do dispositivo.

-Empilhar múltiplas matrizes para criar arquiteturas 3D, como geradores de imagens de três camadas, levou a uma mudança de paradigma no design de sensores,- disse Renan Bouis, autor principal do artigo, -Desenvolvimento de processo de desbaste traseiro para TSV de alta densidade em uma integração de 3 camadas- . –

-A comunicação entre os diferentes níveis requer tecnologias avançadas de interconexão, um requisito que a ligação híbrida atende devido ao seu passo muito fino na faixa do micrômetro e até mesmo submicrômetro”, disse ele. -A alta densidade através do silício via (HD TSV) tem uma densidade semelhante que permite a transmissão de sinal através das camadas intermediárias. Ambas as tecnologias contribuem para a redução do comprimento do fio, um fator crítico para melhorar o desempenho das arquiteturas empilhadas em 3D.”

‘Precisão e compactação incomparáveis’

Os três projetos aplicaram o trabalho anterior do instituto no empilhamento de três wafers de silício de 300 mm usando esses blocos tecnológicos.

-Os artigos apresentam os principais blocos tecnológicos que são obrigatórios para a fabricação de geradores de imagens inteligentes multicamadas 3D, capazes de atender a novas aplicações que exigem IA incorporada”, disse Eric Ollier, gerente de projeto da CEA-Leti e diretor do programa Smart Imager da IRT Nanoelec. O CEA -O instituto Leti é um grande parceiro da IRT Nanoelec.

-A combinação de ligação híbrida com TSVs HD em sensores de imagem CMOS poderia facilitar a integração de vários componentes, como matrizes de sensores de imagem, circuitos de processamento de sinal e elementos de memória, com precisão e compacidade incomparáveis”, disse Stéphane Nicolas, principal autor do artigo. -Demonstrador de ligação híbrida Cu-Cu de passo fino de 3 camadas com TSV de alta densidade para aplicações avançadas de sensor de imagem CMOS,” que foi escolhido como um dos artigos de destaque da conferência.-

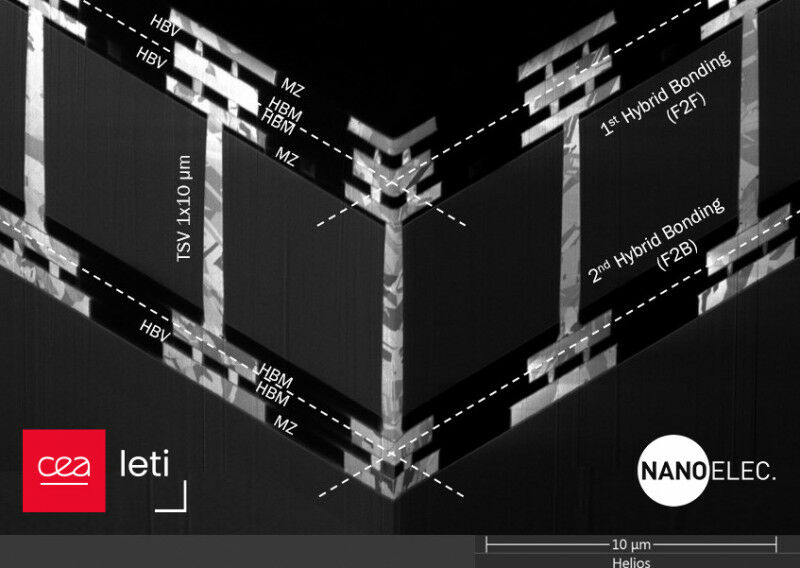

-O projeto desenvolveu um veículo de teste de três camadas que apresentava duas interfaces de ligação híbrida Cu-Cu incorporadas, face a face (F2F) e face-to-back (F2B), e com um wafer contendo TSVs de alta densidade.

Ollier disse que o veículo de teste é um marco importante porque demonstra a viabilidade de cada bloco tecnológico e também a viabilidade do fluxo do processo de integração.

-Este projeto prepara o terreno para trabalhar na demonstração de um sensor de imagem CMOS inteligente de três camadas totalmente funcional, com IA de ponta capaz de abordar segmentação semântica de alto desempenho e aplicações de detecção de objetos “, disse ele.

No ECTC 2023, os cientistas do CEA-Leti relataram um veículo de teste de duas camadas combinando um TSV HD de 10 mícrons de altura e 1 mícron de diâmetro e tecnologia de ligação híbrida altamente controlada, ambos montados na configuração F2B. O trabalho recente encurtou o HD TSV para seis mícrons de altura, o que levou ao desenvolvimento de um veículo de teste de duas camadas exibindo desempenho elétrico de baixa dispersão e permitindo uma fabricação mais simples.

‘Redução de 40 por cento na resistência elétrica’

–

-Nosso TSV HD de cobre de 1 por 6 mícron oferece melhor resistência elétrica e desempenho de isolamento em comparação com nosso TSV HD de 1 por 10 mícron, graças a um processo de desbaste otimizado que nos permitiu reduzir a espessura do substrato com boa uniformidade, ” disse Stéphan Borel, principal autor do artigo, -Baixa resistência e alto isolamento HD TSV para sensores de imagem CMOS de 3 camadas”.

-Essa altura reduzida levou a uma diminuição de 40% na resistência elétrica, proporcionalmente à redução do comprimento. A redução simultânea da relação de aspecto aumentou a cobertura do degrau do revestimento de isolamento, levando a uma melhor resistência à tensão”, acrescentou.

-Com estes resultados, a CEA-Leti é agora claramente identificada como líder global neste novo campo dedicado à preparação da próxima geração de geradores de imagens inteligentes,- explicou Ollier. -Esses novos geradores de imagens inteligentes multicamadas 3D com IA de ponta implementada no próprio sensor serão realmente um avanço no campo de imagem, porque a IA de ponta aumentará o desempenho do gerador de imagens e permitirá muitas novas aplicações.-

Seção transversal FIB-SEM 3D de toda a estrutura do veículo de teste – o passo é de 6 µm para as almofadas de ligação híbridas – As dimensões do HD TSV são 1×10 µm